#include <NAFE33352.h>

Classes | |

| class | LogicalChannel |

| class | DAC |

Public Member Functions | |

| NAFE33352_Base (bool spi_addr, bool highspeed_variant, int nINT, int DRDY, int SYN, int nRESET, int DRDY_input, int SYNCDAC) | |

| virtual | ~NAFE33352_Base () |

| virtual void | boot (void) |

| virtual void | reset (bool hardware_reset=false) |

| virtual void | open_logical_channel (int ch, uint16_t cc0, uint16_t cc1, uint16_t cc2, uint16_t dummy) |

| virtual void | open_logical_channel (int ch, const uint16_t(&cc)[4]) |

| void | open_dac_output (const uint16_t(&cc)[6]) |

| virtual void | close_logical_channel (int ch) |

| virtual void | close_logical_channel (void) |

| void | enable_logical_channel (int ch) |

| virtual void | start (int ch) |

| virtual void | start (void) |

| virtual void | start_continuous_conversion () |

| virtual void | DRDY_by_sequencer_done (bool flag=true) |

| virtual raw_t | read (int ch) |

| virtual void | read (raw_t *data) |

| virtual void | read (volt_t *data) |

| double | raw2v (int ch, raw_t value) |

| virtual void | dac_out (double vi, double full_scale, uint8_t bit_length) |

| int32_t | dac_code (double a, double full_scale, uint8_t bit_length) |

| virtual void | command (uint16_t com) |

| virtual void | reg (Register16 r, uint16_t value) |

| virtual void | reg (Register24 r, uint32_t value) |

| virtual uint16_t | reg (Register16 r) |

| virtual uint32_t | reg (Register24 r) |

| template<typename T> | |

| uint32_t | bit_op (T rg, uint32_t mask, uint32_t value) |

| uint64_t | part_number (void) |

| uint8_t | revision_number (void) |

| uint64_t | serial_number (void) |

| float | temperature (void) |

| Public Member Functions inherited from AFE_base | |

| AFE_base (bool spi_addr, bool highspeed_variant, int nINT, int DRDY, int SYN, int nRESET, int DRDY_input, int SYNCDAC) | |

| virtual | ~AFE_base () |

| virtual void | begin (void) |

| virtual void | set_DRDY_callback (callback_fp_t fnc) |

| virtual raw_t | start_and_read (int ch) |

| template<typename T> | |

| void | start_and_read (T data) |

| double | raw2uv (int ch, raw_t value) |

| double | raw2mv (int ch, raw_t value) |

| double | drdy_delay (int ch) |

| double | drdy_delay (void) |

| int | enabled_logical_channels (void) |

| void | use_DRDY_trigger (bool use=true) |

| Public Member Functions inherited from SPI_for_AFE | |

| void | txrx (uint8_t *data, int size) |

| void | write_r16 (uint16_t reg) |

| void | write_r16 (uint16_t reg, uint16_t val) |

| uint16_t | read_r16 (uint16_t reg) |

| void | write_r24 (uint16_t reg, uint32_t val) |

| int32_t | read_r24 (uint16_t reg) |

| void | burst (uint32_t *data, int length, int width=3) |

Public Attributes | |

| LogicalChannel | logical_channel [16] |

| DAC | dac |

Static Public Attributes | |

| static constexpr double | on_board_shunt_resister = 50.00 |

| static constexpr double | pga_gain [] = { 1.00, 16.00 } |

| Static Public Attributes inherited from AFE_base | |

| static AFE_base * | instance = nullptr |

Private Member Functions | |

| double | calc_delay (int ch) |

| void | channel_info_update (uint16_t value) |

Additional Inherited Members | |

| Protected Member Functions inherited from AFE_base | |

| int | bit_count (uint32_t value) |

| void | default_drdy_cb () |

| virtual void | init (void) |

| int | wait_conversion_complete (double delay=-1.0) |

| Static Protected Member Functions inherited from AFE_base | |

| static void | static_default_drdy_cb () |

| static void | DRDY_cb () |

| Protected Attributes inherited from AFE_base | |

| bool | dev_add |

| bool | highspeed_variant |

| int | pin_nINT |

| int | pin_DRDY |

| int | pin_SYN |

| int | pin_nRESET |

| int | pin_DRDY_input |

| int | pin_SYNCDAC |

| int | enabled_channels |

| uint8_t | sequence_order [16] |

| double | coeff_V [16] |

| int | mux_setting [16] |

| double | ch_delay [16] |

| double | total_delay |

| uint32_t | drdy_count |

| volatile bool | drdy_flag |

| Static Protected Attributes inherited from AFE_base | |

| static double | delay_accuracy = 1.2 |

| static constexpr uint32_t | timeout_limit = 10000000 |

| static callback_fp_t | cbf_DRDY = nullptr |

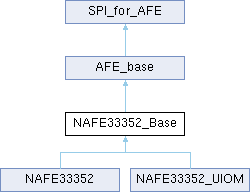

Detailed Description

NXP Analog Front End class library for MCX

Copyright: 2026 Tedd OKANO Released under the MIT license

Definition at line 16 of file NAFE33352.h.

Member Typedef Documentation

◆ ch_setting_t

| using NAFE33352_Base::ch_setting_t = uint16_t[ 4 ] |

Definition at line 19 of file NAFE33352.h.

Member Enumeration Documentation

◆ Command

| enum NAFE33352_Base::Command : uint16_t |

Definition at line 355 of file NAFE33352.h.

◆ GainPGA

| enum NAFE33352_Base::GainPGA : uint8_t |

| Enumerator | |

|---|---|

| G_PGA_x_1_0 | |

| G_PGA_x16_0 | |

Definition at line 249 of file NAFE33352.h.

◆ IN_SEL

| enum NAFE33352_Base::IN_SEL : uint8_t |

| Enumerator | |

|---|---|

| VCM_VCM | |

| AIP_AIN | |

| AIP_VSNS | |

| GPIO0_GPIO1 | |

| AIP | |

| AIN | |

| ISNS | |

| VSNS | |

| TIA | |

| GPIO0_VCM | |

| VCM_GPIO1 | |

| REF_BYP__VCM | |

| VCM__REF_BYP | |

| BG | |

| VADD | |

| LDO | |

| VHDD | |

| VHSS | |

| DAC_REF | |

Definition at line 227 of file NAFE33352.h.

◆ Register16

|

strong |

Definition at line 254 of file NAFE33352.h.

◆ Register24

|

strong |

Definition at line 295 of file NAFE33352.h.

Constructor & Destructor Documentation

◆ NAFE33352_Base()

| NAFE33352_Base::NAFE33352_Base | ( | bool | spi_addr, |

| bool | highspeed_variant, | ||

| int | nINT, | ||

| int | DRDY, | ||

| int | SYN, | ||

| int | nRESET, | ||

| int | DRDY_input, | ||

| int | SYNCDAC ) |

Constructor to create a NAFE33352_Base instance

Definition at line 115 of file NAFE33352.cpp.

Referenced by NAFE33352::NAFE33352(), and NAFE33352_UIOM::NAFE33352_UIOM().

◆ ~NAFE33352_Base()

|

virtual |

Destractor

Definition at line 127 of file NAFE33352.cpp.

Member Function Documentation

◆ bit_op()

|

inline |

Register bit operation

overwrite bits i a register

- Parameters

-

reg register specified by Register16 or Register24 member mask mask bits reg value to over write

Definition at line 435 of file NAFE33352.h.

Referenced by close_logical_channel(), DRDY_by_sequencer_done(), and enable_logical_channel().

◆ boot()

|

virtual |

Set system-level config registers

Implements AFE_base.

Definition at line 131 of file NAFE33352.cpp.

◆ calc_delay()

|

private |

Definition at line 278 of file NAFE33352.cpp.

Referenced by open_logical_channel().

◆ channel_info_update()

|

private |

Definition at line 253 of file NAFE33352.cpp.

Referenced by close_logical_channel(), close_logical_channel(), and enable_logical_channel().

◆ close_logical_channel() [1/2]

|

virtual |

Logical channel disable

- Parameters

-

ch logical channel number (0 ~ 15)

Implements AFE_base.

Definition at line 345 of file NAFE33352.cpp.

◆ close_logical_channel() [2/2]

|

virtual |

◆ command()

|

virtual |

- Parameters

-

com "Comand" type or uint16_t value

Definition at line 417 of file NAFE33352.cpp.

Referenced by boot(), calc_delay(), open_logical_channel(), reset(), start(), start(), and start_continuous_conversion().

◆ dac_code()

| int32_t NAFE33352_Base::dac_code | ( | double | a, |

| double | full_scale, | ||

| uint8_t | bit_length ) |

Definition at line 405 of file NAFE33352.cpp.

Referenced by dac_out().

◆ dac_out()

|

virtual |

Definition at line 400 of file NAFE33352.cpp.

◆ DRDY_by_sequencer_done()

|

virtual |

DRDY event select

- Parameters

-

set true for DRDY by sequencer is done

Implements AFE_base.

Definition at line 375 of file NAFE33352.cpp.

Referenced by boot().

◆ enable_logical_channel()

|

virtual |

Logical channel enable

- Parameters

-

ch logical channel number (0 ~ 15)

Implements AFE_base.

Definition at line 337 of file NAFE33352.cpp.

Referenced by open_logical_channel().

◆ open_dac_output()

| void NAFE33352_Base::open_dac_output | ( | const uint16_t(&) | cc[6] | ) |

Definition at line 171 of file NAFE33352.cpp.

◆ open_logical_channel() [1/2]

|

virtual |

Configure logical channel

- Parameters

-

ch logical channel number (0 ~ 15) cc array for AI_CONFIG0, AI_CONFIG1, AI_CONFIG2 and dummy values

Implements AFE_base.

Definition at line 178 of file NAFE33352.cpp.

◆ open_logical_channel() [2/2]

|

virtual |

Configure logical channel

- Parameters

-

ch logical channel number (0 ~ 15) cc0 16bit value to be set AI_CONFIG0 register (0x20) cc1 16bit value to be set AI_CONFIG1 register (0x21) cc2 16bit value to be set AI_CONFIG2 register (0x22) dummy dummy variable to keep compatibility over AFE devices

Implements AFE_base.

Definition at line 330 of file NAFE33352.cpp.

Referenced by open_logical_channel().

◆ part_number()

| uint64_t NAFE33352_Base::part_number | ( | void | ) |

◆ raw2v()

|

inlinevirtual |

Convert raw output to volt

- Parameters

-

ch logical channel number to select its gain coefficient value ADC read value

Implements AFE_base.

Definition at line 212 of file NAFE33352.h.

◆ read() [1/3]

|

virtual |

Read ADC for single channel

- Parameters

-

ch logical channel number (0 ~ 15)

Implements AFE_base.

Definition at line 380 of file NAFE33352.cpp.

Referenced by read().

◆ read() [2/3]

|

virtual |

Read ADC for all channel

- Parameters

-

data_ptr pointer to array to store ADC data

Implements AFE_base.

Definition at line 385 of file NAFE33352.cpp.

◆ read() [3/3]

|

virtual |

Read ADC for all channel

- Parameters

-

data_ptr pointer to array to store ADC data

Implements AFE_base.

Definition at line 390 of file NAFE33352.cpp.

◆ reg() [1/4]

|

virtual |

Read register

Reads register. Register width is selected by reg type (Register16 ot Register24)

- Parameters

-

reg register specified by Register16 member

- Returns

- readout value

Definition at line 432 of file NAFE33352.cpp.

◆ reg() [2/4]

|

virtual |

Write register

Writes register. Register width is selected by reg type (Register16 ot Register24)

- Parameters

-

reg register specified by Register16 member

Definition at line 422 of file NAFE33352.cpp.

Referenced by bit_op(), boot(), calc_delay(), close_logical_channel(), dac_out(), open_dac_output(), open_logical_channel(), part_number(), read(), reset(), revision_number(), serial_number(), and temperature().

◆ reg() [3/4]

|

virtual |

Read register

Reads register. Register width is selected by reg type (Register16 ot Register24)

- Parameters

-

reg register specified by Register24 member

- Returns

- readout value

Definition at line 437 of file NAFE33352.cpp.

◆ reg() [4/4]

|

virtual |

Write register

Writes register. Register width is selected by reg type (Register16 ot Register24)

- Parameters

-

reg register specified by Register24 member

Definition at line 427 of file NAFE33352.cpp.

◆ reset()

|

virtual |

◆ revision_number()

| uint8_t NAFE33352_Base::revision_number | ( | void | ) |

◆ serial_number()

| uint64_t NAFE33352_Base::serial_number | ( | void | ) |

Read serial number

- Returns

- serial number

Definition at line 452 of file NAFE33352.cpp.

Referenced by serial_number().

◆ start() [1/2]

|

virtual |

Start ADC

- Parameters

-

ch logical channel number (0 ~ 15)

Implements AFE_base.

Definition at line 359 of file NAFE33352.cpp.

◆ start() [2/2]

|

virtual |

◆ start_continuous_conversion()

|

virtual |

◆ temperature()

| float NAFE33352_Base::temperature | ( | void | ) |

Member Data Documentation

◆ dac

| DAC NAFE33352_Base::dac |

Definition at line 143 of file NAFE33352.h.

Referenced by NAFE33352_Base().

◆ logical_channel

| LogicalChannel NAFE33352_Base::logical_channel[16] |

16 LogicalChannel instance array

Definition at line 74 of file NAFE33352.h.

Referenced by NAFE33352_Base().

◆ on_board_shunt_resister

|

staticconstexpr |

Definition at line 20 of file NAFE33352.h.

Referenced by raw2v().

◆ pga_gain

|

staticconstexpr |

Definition at line 225 of file NAFE33352.h.

The documentation for this class was generated from the following files:

Generated by